Quantum Gates

This section studies quantum gates. As the basis, we begin with bit and qubit. We then discuss classical gates, reversible gates and quantum gates in turn. Last, we introduce the Bell circuit and its two applications, i.e., superdense coding and quantum teleportation.

Bits and Qubits

A bit is a unit of information describing a two-dimensional classical system.

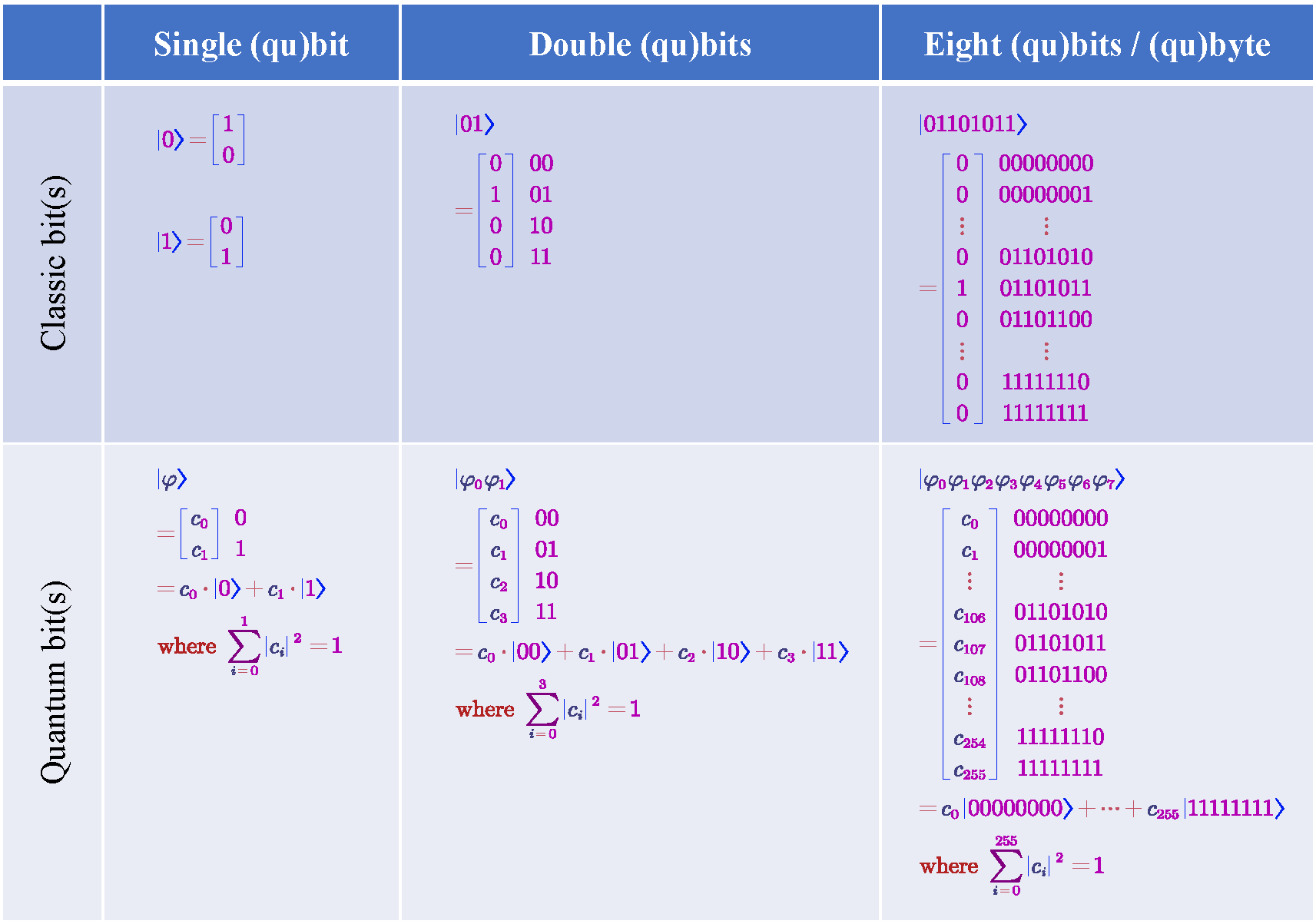

Since a two-dimensional classical system has two orthogonal states, hence the bit and bit can be represented as two binary vectors, i.e., where bit-0 and bit-1 equal to and for the convenience of the following discussion.

A quantum bit or a qubit is a unit of information describing a two- dimensional quantum system.

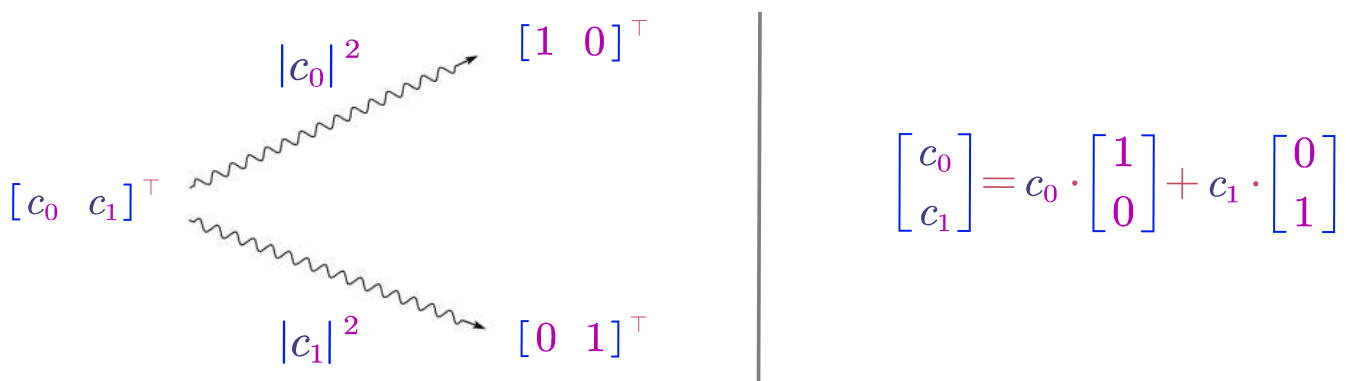

The only difference between the above two definitions is the property of the two-dimensional system. The former is a classic system, while the latter is a quantum system. This means that the state of a qubit lies in the complex vector space satisfying the normalization constraint, i.e., where . Whenever we measure a qubit, it automatically becomes a bit with corresponding collapse probability of for bit and for bit as shown in Figure 1.1. So we shall never "see" a general qubit.

The byte is a unit of digital information that most commonly consists of eight bits.

For example, given a byte including eight bits , the vector representation of these eight bits is: , , , , , , , . Recall the tensor product in composite system, the state of a byte equals to , which is a discrete element of the complex vector space .

The qubyte is a unit of quantum information that consists of eight qubits.

Similar, the state of a qubyte is the tensor product of eight qubits, i.e., , wihch is a continues element of the complex vector space .

The state vectors of single (qu)bit, double (qu)bits and (qu)byte are shown in Figure 1.2. Let's compare the byte and qubyte, both of them are represented as a -dimensional vector. But the former, classic byte, contains only binary numbers, while the latter, quantum byte, contains complex numbers. This difference indicates qubyte is much more informative than the classic byte.

Classic Gates

Matrix representation. Classical logical gates are ways of manipulating bits. This section studies classical gates from the point of view of matrices. As stated in Section 1.1, we represent input bits as a vector and output bits as a vector. How should we represent our logical gates? When one multiplies a matrix with a vector, the result is a vector. In symbols:

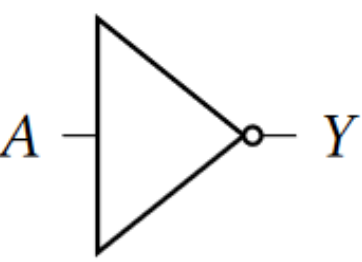

ex:NOT-gate Consider the NOT gate:

NOT gate takes as input one bit, or a vector, and outputs one bit, or a vector. NOT of equals and NOT of equals . Consider the matrix This matrix satisfies

ex:AND-gate Consider the AND gate:

The AND gate accepts two bits and outputs one bit, hence we need a matrix. Consider the matrix This matrix satisfies and

ex:OR-gate Consider the OR gate:

The OR gate similarly accepts two bits and outputs one bit, hence can be represented by a matrix. This matrix satisfies and

NAND-gate Consider the NAND gate:

The NAND gate similarly accepts two bits and outputs one bit, hence can be represented by a matrix. This matrix satisfies

Sequential operation. The way of thinking of NAND brings to light a general situation. When we perform a computation, we often have to carry out one operation followed by another. We call this procedure performing sequential operations. Take Figure 5.3 as an example, if A an operation with input bits and output bits, its matrix will be of size . Say, B takes the outputs of A as input and outputs bits, then B is represented by a matrix, and performing one operation sequentially followed by another operation corresponds to , which is a matrix.

Parallel operation. Besides sequential operations, there are parallel operations as shown in Figure 5.3. Here we have A acting on some bits and B on others. This will be represented by . Let us be exact with the number of inputs and the number of outputs. A will be of size . B will be of size , is of size .

Mixed operation. Take Figure 5.3 as an example, let A be an operation that takes inputs and gives outputs. Let B take of these outputs and leave the other outputs alone. B outputs bits. A is a matrix. B is a matrix. As nothing should be done to the bits, we might represent this as the identity matrix . We do not draw any gate for the identity matrix. The entire circuit can be represented by the following matrix:

Consider the circuit:

This is represented by Let us see how the operations look like as matrices. We first calculate the parallel part: And then we calculate the whole circuit:

Consider the circuit:

This is represented by Let us see how the operations look like as matrices. We first calculate the parallel part: And then we calculate the whole circuit

:

Reversible Gates

In the quantum world, all operations that are not measurements are reversible and are represented by unitary matrices. The AND operation is not reversible. Given an output of from AND, one cannot determine if the input was , , or . So from an output of the AND gate, one cannot determine the input and hence AND is not reversible. In contrast, the NOT gate and the identity gates are reversible.

Reversible gates have a history that predates quantum computing. In the 1960s, Rolf Landauer analyzed computational processes and showed that erasing information, as opposed to writing information, is what causes energy loss and heat. This notion has come to be known as the Landauer's principle.

We have found that erasing information is an irreversible, energy-dissipating operation. In the 1970s, Charles H. Bennett continued along these lines of thought. If erasing information is the only operation that uses energy, then a computer that is reversible and does not erase would not use any energy. Bennett started working on reversible circuits and programs.

A reversible circuit has exactly as many outputs as inputs. Each input can be reconstructed from the output; no bits are lost, so reversible circuits will not give off heat from bit loss.

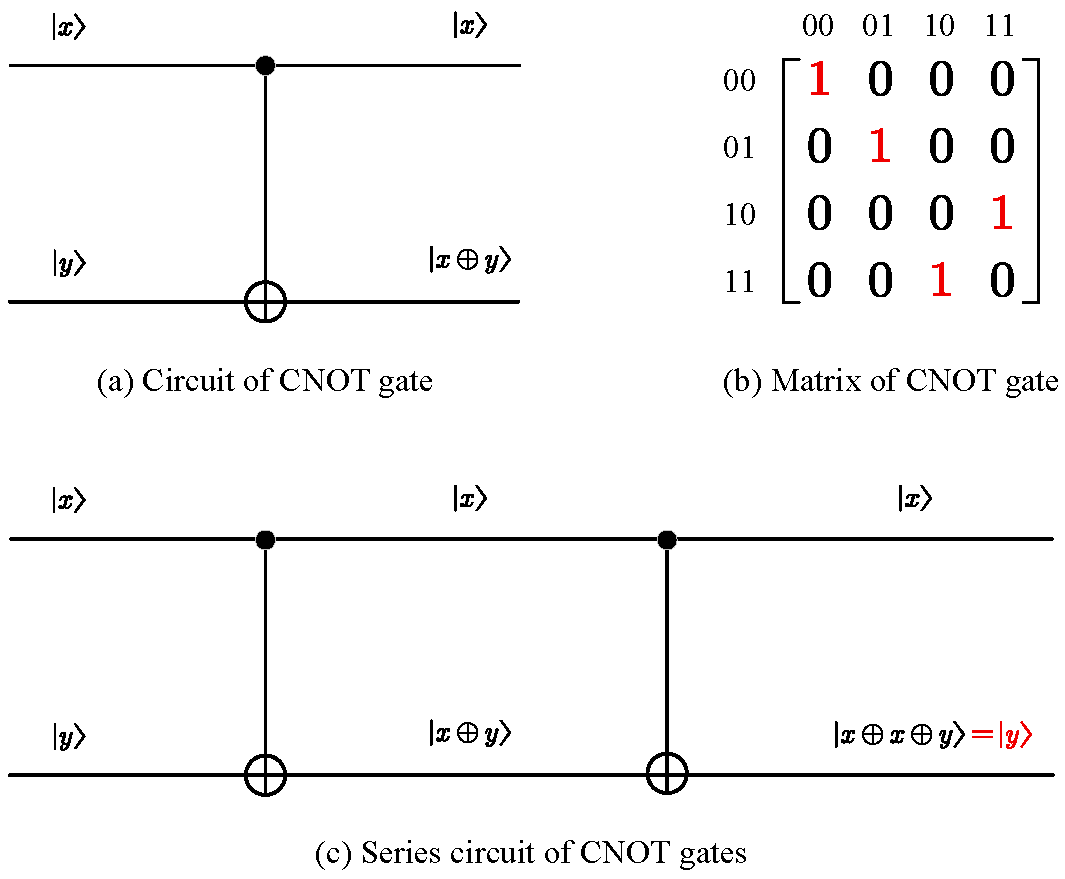

CNOT gate

What examples of reversible gates are there? We have already seen that the identity gate and NOT gates are reversible. What else is there? Consider the following controlled-NOT gate shown in Figure 1.4(a):

This gate has two inputs and two outputs. The top input is the control bit. It controls what the output will be. If , then the bottom output of will be the same as the input. If , then the bottom output will be the opposite. If we write the top qubit first and then the bottom qubit, then the controlled-NOT gate takes to , where is the binary "exclusive or" operation. The matrix that corresponds to this reversible gate is shown in Figure 5.4.

CNOT gate can be reversed by itself as shown in Figure 5.4(c). State goes to , which further goes to . This last state is equal to because is associative. Because is always equal to , this state reduces to the original .

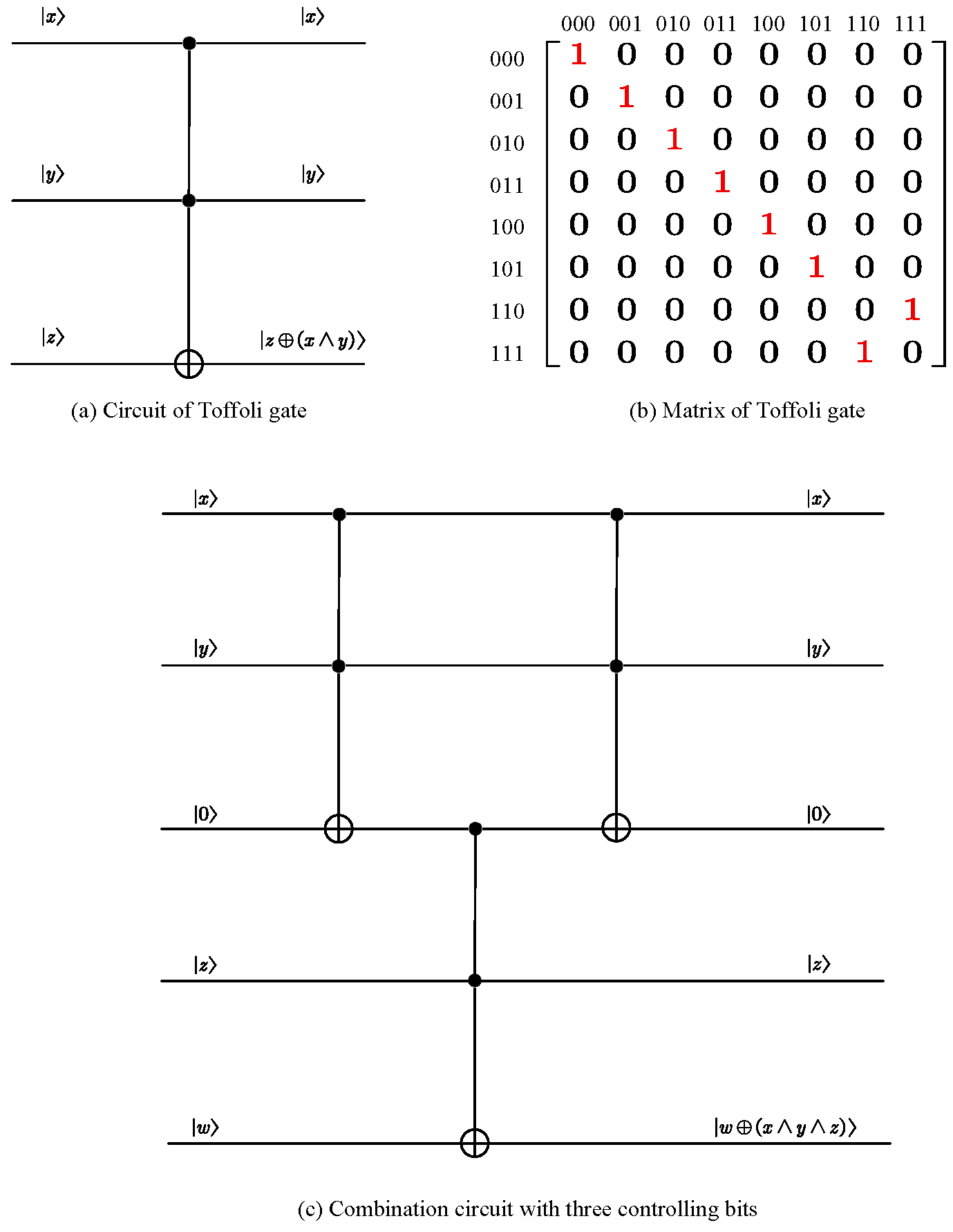

Toffoli gate

Toffoli gate extends CNOT gate's function by using two controlling bits. The bottom bit flips only when both of the top two bits are in state . We can write this operation as taking state to . The circuit and matrix representations of Toffoli gate is shown in Figure 5.5 (a) and (b).

The NOT gate has no controlling bit, the CNOT gate has one controlling bit, and the Toffoli gate has two controlling bits. We can go on with this by with the combination circuit shown in Figure 5.5(c).

One reason why the Toffoli gate is interesting is that it is universal. In other words, with copies of the Toffoli gate, we can make any logical gate. In order to see that the Toffoli gate is universal, we will show that it can be used to make both the AND and NOT gates as shown in Figure 5.6 (a) and (b). Specifically, the AND gate is obtained by setting the bottom input to , and the bottom output will then be . The NOT gate is obtained by setting the top two inputs to , and bottom output will be .

Moreover, in order to construct all gates, we must also have a way of producing a fanout of values. In other words, a gate is needed that inputs a value and outputs two of the same values. This can be obtained by setting to and to . This makes the output .

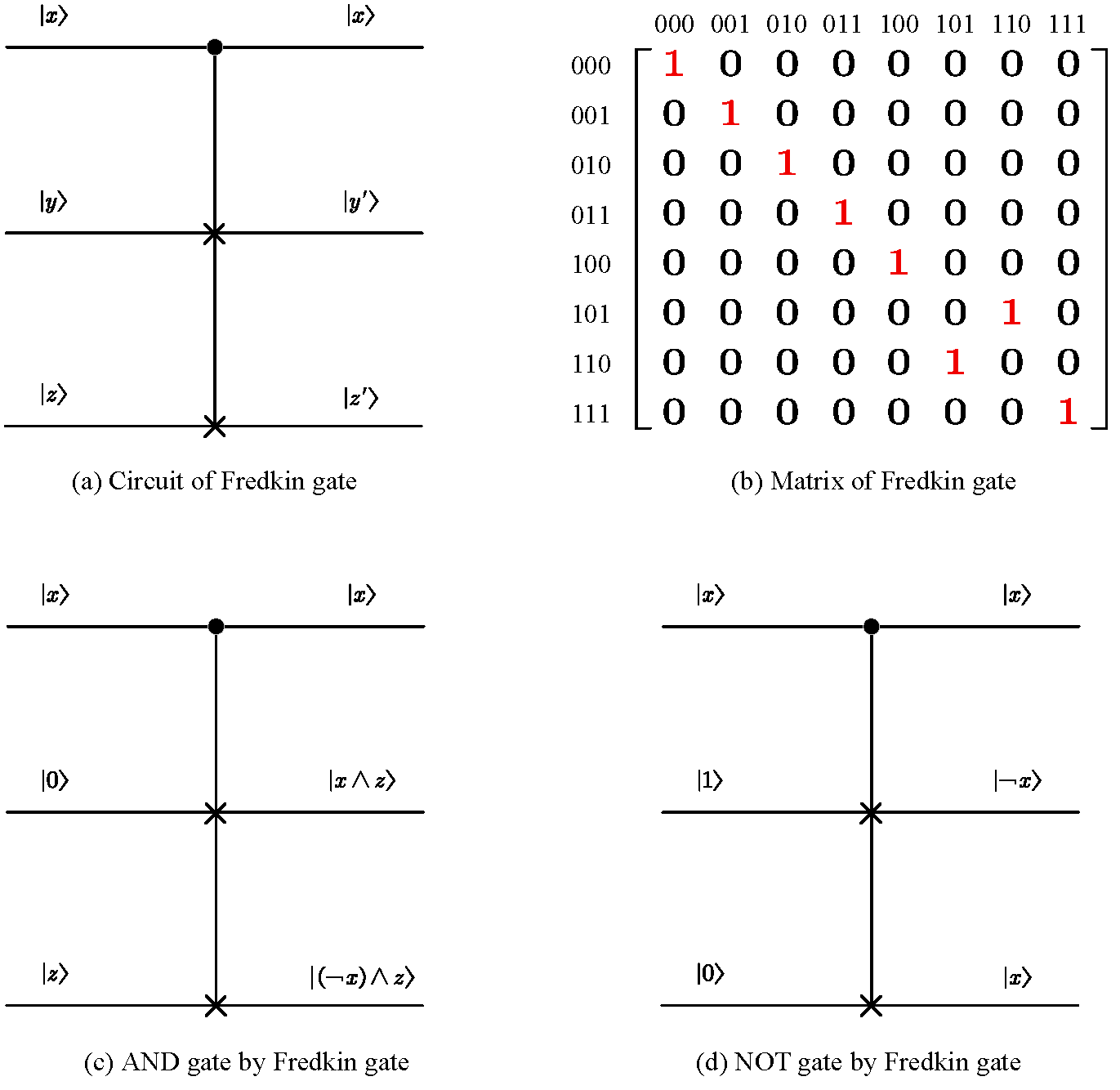

Fredkin gate

Another interesting reversible gate is the Fredkin gate. The Fredkin

gate also has three inputs and three outputs as shown in Figure

1.7 (a).

The top input is the control input. The output is always the

same . If is set to , then

and , i.e., the values stay the

same. If, on the other hand, the control is set to ,

then the outputs are reversed: and

. In short, and

.

The matrix that corresponds to the Fredkin gate is shown in Figure 5.7 (b), from which we can see that the Fredkin gate is its own inverse. The Fredkin gate is also universal. By setting to as shown in Figure 5.7(c). The NOT gate and the fanout gate can be obtained by setting to and to as shown in Figure 5.7(d).

So both the Toffoli and the Fredkin gates are universal. Not only are both reversible gates; a glance at their matrices indicates that they are also unitary.

Quantum Gates

quantum gate is simply an operator that acts on qubits. Such operators will be represented by unitary matrices.

We have already worked with some quantum gates such as the identity operator I, the Hadamard gate H, the NOT gate, the CNOT gate, the Toffoli gate, and the Fredkin gate. What else is there? Here we discuss some important quantum gates:

-

Pauli matrices. They occur everywhere in quantum mechanics and quantum computing. Note that the X matrix is nothing more than our NOT matrix.

-

Square root of NOT. It is a one-qubit quantum gate and is denoted as . The matrix representation of this gate is

-

Hardmard gates. It is defined as The Hardmard gate has two important properties in quantum algorithm. First, we can transition into superposition from classic state through Hardmard gate. Second, we can transition out of superposition without measurement with the help of Hardmard gate.

-

Phase shift gate. It is defined as This gate performs the following operation on an arbitrary qubit: This corresponds to a rotation that leaves the latitude alone and just changes the longitude. The new state of the qubit will remain unchanged. Only the phase will change.

-

Controlled-U gate. It is equivalent to an IF--THEN statement. If a certain (qu)bit is true, then a particular operation should be performed, otherwise the operation is not performed. For every -qubit unitary operation U, we can create a unitary -qubit operation controlled-U or :

-

Deutsch gate. It is very similar to the Toffoli gate. If the inputs and are both , then the phase shift operation will act on the input. Otherwise, the will simply be the same as the . When is not a rational multiple of , by itself is a universal three-qubit quantum gate. In other words, will be able to mimic every other quantum gate.

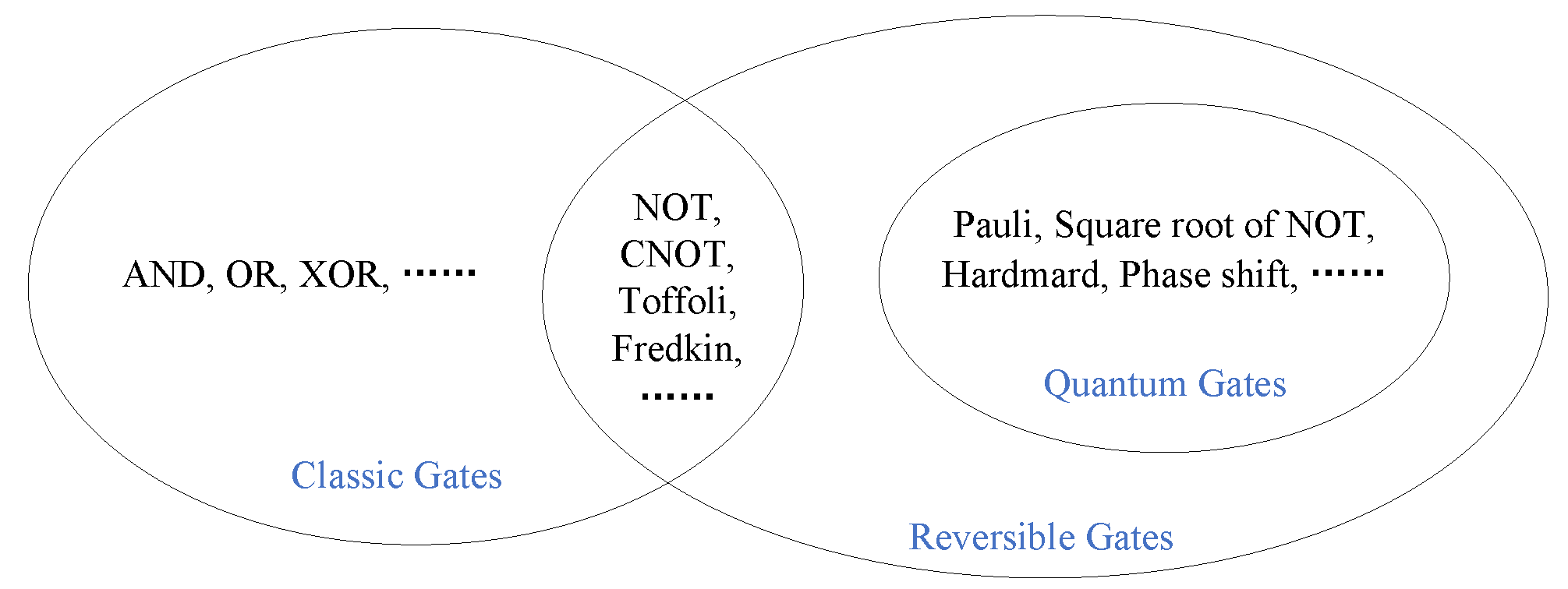

Up to now, we have discussed classic gates, reversible gates and quantum gates. Their relationship can be illustrated by the following Figure 5.8.